|

|

|

Главная страница Межпроцессное взаимодействие (состязание) Формат селектора сознательно продуман так, чтобы упростить определение местоположения дескриптора. Сначала выбирается локальная или глобальная таблица дескрипторов, основываясь на бите 2 селектора. Затем селектор копируется во внутренний рабочий регистр, и три младших бита сбрасываются в нули. Наконец, к нему прибавляется адрес одной из таблиц, с целью получить прямой указатель на дескриптор. Например, селектор 72 ссылается на запись 9 в глобальной таблице дескрипторов, расположенную по адресу в таблице GDT+72. Теперь проследим шаги, с помощью которых пара селектор-смещение преобразуется в физический адрес. Как только микропрограмма узнает, какой сегментный регистр используется, она может найти в своих внутренних регистрах полный дескриптор, соответствующий этому селектору. Если сегмент не существует (селектор равен 0) или в данный момент выгружен, происходит прерывание. Затем микропрограмма проверяет, выходит ли смещение за пределы сегмента, в случае чего также возникает прерывание. Логически, в дескрипторе просто должно существовать 32-разрядное поле, дающее размер сегмента, но там доступны только 20 бит, поэтому действует другая схема. Если поле Gbit (granularity - глубина детализации) равно О, то поле Limit (предел) содержит точный размер сегмента, до 1 Мбайт. Если гранулярность равна 1, поле Limit дает размер сегмента в страницах вместо байтов. Размер страницы в системе Pentium фиксирован на величине 4 Кбайт, поэтому 20 бит достаточно для сегментов размером до 2 байт. Предположим, что сегмент находится в памяти, а смещение попало в нужный интервал. Тогда Pentium прибавляет 32-разрядное поле Base (база) в дескрипторе к смещению, формируя то, что называется линейным адресом, как показано на рис. 4.27. Поле Base разбито на три части, которые разбросаны по дескриптору для совместимости с процессором Intel 80286, где поле Base имеет только 24 бита. В сущности, поле Base позволяет каждому сегменту начинаться в произвольном месте внутри 32-разрядного линейного адресного пространства. Селектор Смещение Дескриптор

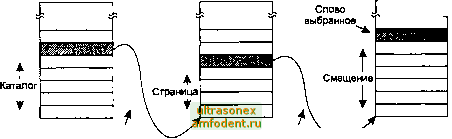

32-разрядный линейный адрес Рис. 4.27. Преобразование пары селектор-смещение в физический адрес Если разбиение на страницы блокировано (с помощью бита в глобальном управляющем регистре), линейный адрес интерпретируется как физический адрес и посылается в память для чтения или записи. Таким образом, при отключенной страничной схеме памяти мы получаем чистую схему сегментации с базовым адресом каждого сегмента, выдаваемым его дескриптором. Сегментам разрешено перекрываться случайным образом, возможно потому, что контроль за тем, чтобы они не пересекались, мог бы причинить достаточно хлопот и занял бы слишком много времени. С другой стороны, если доступна страничная подкачка, линейный адрес интерпретируется как виртуальный адрес и отображается на физический адрес с помощью таблицы страниц практически так же, как в наших предыдущих примерах. Единственная серьезная трудность заключается в том, что при 32-разрядном виртуальном адресе и странице размером 4 Кбайт сегмент может содержать 1 млн страниц, поэтому используется двухуровневое отображение с целью уменьшения размера таблицы страниц для маленьких сегментов. У каждой работающей программы есть страничный каталог, состоящий из 1024 32-разрядных записей. Он расположен по адресу, хранящемуся в глобальном регистре. Каждая запись в каталоге ссылается на таблицу страниц, также содержащую 1024 32-разрядных записей. Записи в таблицах страниц, в свою очередь, указывают на страничные блоки. Эта организация продемонстрирована на рис. 4.28. Биты Линейный адрес 10 Каталог Страница Смещение Страничный каталог 1024 записей Таблица страниц Страничный блок  Запись каталога указывает на таблицу каталога Запись в таблица страниц указывает на слово Рис. 4.28. Отображение линейного адреса на физический адрес На рис. 4.28, а мы видим линейный адрес, разделенный на три поля: Каталог, Страница и Смещение. Поле Каталог используется как индекс в страничном каталоге, определяющий расположение указателя на правильную таблицу страниц. Затем обрабатывается поле Страница в качестве индекса в таблице страниц, с целью найти физический адрес страничного блока. И наконец, чтобы получить физический адрес требуемого байта или слова, к адресу страничного блока прибавляется последнее поле Смещение. Каждая запись в таблице имеет размер 32 бита, двадцать из которых содержат номер страничного блока. Остальные биты - это биты доступа и грязный бит, задаваемые аппаратурой для операционной системы, биты защиты и другие полезные биты. Каждая таблица страниц включает в себя записи для 1024 страничных блоков размером по 4 Кбайт, таким образом, одна таблица страниц управляет четырьмя мегабайтами памяти. Сегмент, длина которого меньше 4 М, будет иметь страничный каталог с единственной записью - указателем на его единственную таблицу страниц. Следовательно, в случае короткого сегмента на поддержку таблиц страниц расходуется только две страницы вместо миллиона, который был бы нужен в одноуровневой таблице страниц. Чтобы избежать повторных обращений к памяти, система Pentium, как и MULTICS, имеет небольшой буфер быстрого преобразования адреса (TLB), который напрямую отображает наиболее часто используемые комбинации Каталог-Страница на физический адрес страничного блока. Только когда текущая комбинация отсутствует в TLB, действительно выполняется механизм, показанный на рис. 4.28, и TLB обновляется. Система обладает хорошей производительностью до тех пор, пока обращения к отсутствующим страницам в TLB происходят относительно редко. Также следует отметить, что когда некоторые приложения не требуют сегментации, а довольствуются единым, разбитым на страницы 32-разрядным адресным пространством, эта модель все равно работает. Все сегментные регистры могут быть настроены тем же самым селектором, в дескрипторе которого поле Base = О и поле Limit установлено на максимум. Тогда, при использовании единственного адресного пространства, смещение команды будет линейным адресом - в сущности, это обычная страничная организация памяти. Фактически все современные операционные системы для компьютера Pentium работают таким образом. Система OS/2 была единственной, которая использовала всю мощь архитектуры диспетчера памяти (MMU) фирмы Intel. В конце концов, кто-то должен похвалить разработчиков системы Pentium. При поставленных перед ними противоречивых задачах - реализовать чистую страничную организацию памяти, чистое сегментирование и страничные сегменты, и в то же время обеспечить совместимость с 286-м процессором, а кроме того, сделать все это эффективно, - результирующая структура удивительно проста и понятна. Мы, хотя и кратко, но целиком описали полную архитектуру виртуальной памяти системы Pentium, и теперь следует сказать несколько слов о защите, так как эта тема тесно связана с виртуальной памятью. Как схема виртуальной памяти, так и система защиты на Pentium близка по модели к системе MULTICS. Pentium поддерживает четыре уровня защиты, где уровень О является наиболее привилегированным, а уровень 3 - наименее привилегированным. Они показаны

|

|

© 2000 - 2025 ULTRASONEX-AMFODENT.RU.

Копирование материалов разрешено исключительно при условии цититирования. |